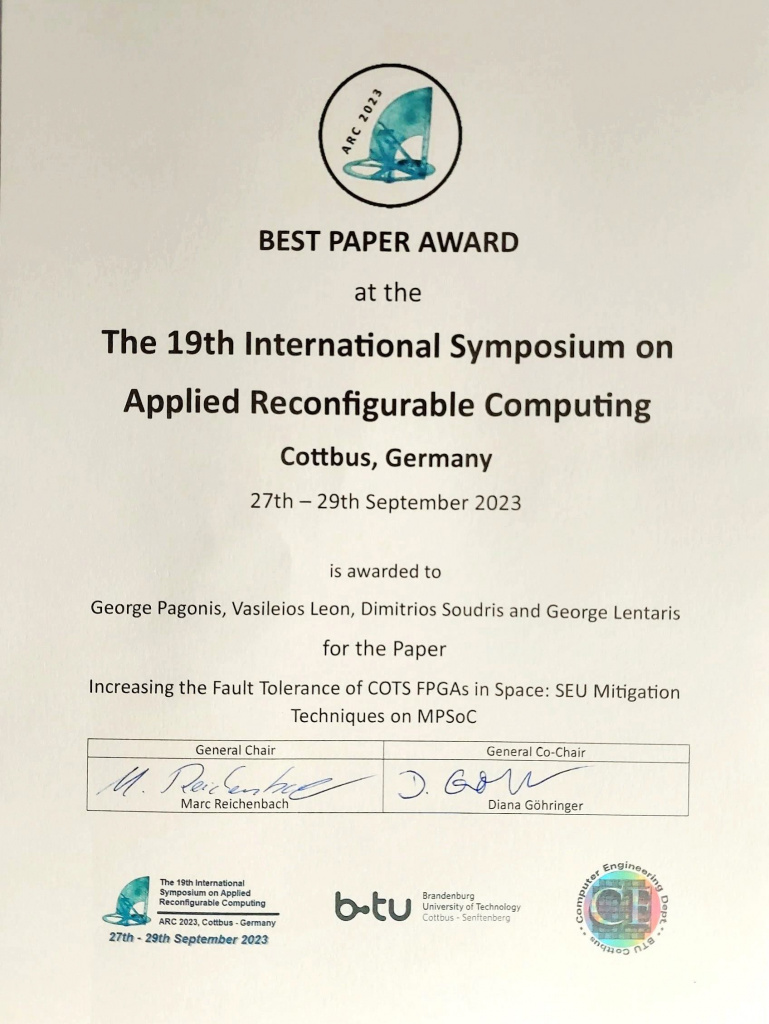

NTUA-ECE MicroLab received the Best Paper Award in the 19th International Symposium on Applied Reconfigurable Computing (ARC)

We are pleased to announce that the paper entitled “Increasing the Fault Tolerance of COTS FPGAs in Space: SEU Mitigation Techniques on MPSoC” received the Best Paper Award in the 19th International Symposium on Applied Reconfigurable Computing (ARC) that was held on September 27-29, 2023 in Cottbus, Germany.

The award-winning paper was co-authored by George Pagonis (National Technical University of Athens), Dr. Vasileios Leon (National Technical University of Athens), Prof. Dimitrios Soudris (National Technical University of Athens), and Prof. George Lentaris (University of West Attica).

Short Abstract: The increasing need for more powerful onboard computing in space applications contributes in a shift towards the use of Commercial-Off-The-Shelf (COTS) accelerators for payload processing, which offer superior performance compared to traditional radiation-hardened devices. To address the reliability concerns associated with the use of COTS accelerators, this paper investigates and evaluates fault-tolerance techniques for the UltraScale+ MPSoC FPGA, which is being considered into multiple research and industrial space avionics. For testing purposes, as a representative DSP circuit, we develop in parametric VHDL and modify a custom Fast Fourier Transform (FFT) kernel. On the accelerator side, the proposed techniques include temporal, spatial, and hybrid redundancy, as well as application-specific triple modular redundancy. On the system side, partial and full reconfiguration methods are used to correct faulty components. The paper also explores the fault resilience of different computational FPGA blocks (i.e., LUTs and DSPs) when implementing the key processing elements. The results show that the use of DSPs is beneficial for decreasing downtime compared to the respective LUT implementation. Our best approach results in a reduction of downtime by 95% and 65% for the 8-point and 32-point FFT, respectively, when compared to the baseline implementation without fault tolerance.

Conference Link: https://arc2023.org/

Paper Link: https://link.springer.com/chapter/10.1007/978-3-031-42921-7_15