PhD thesis defense to be held on April 28, 2023, at 14:00 (New ECE Building, Room B.1.14)

Picture Credit: Dimitrios Baxevanakis

Thesis title: Distortion Estimation Methodologies and Architectures for High Linearity and Efficiency Power Amplifiers in CMOS Technologies

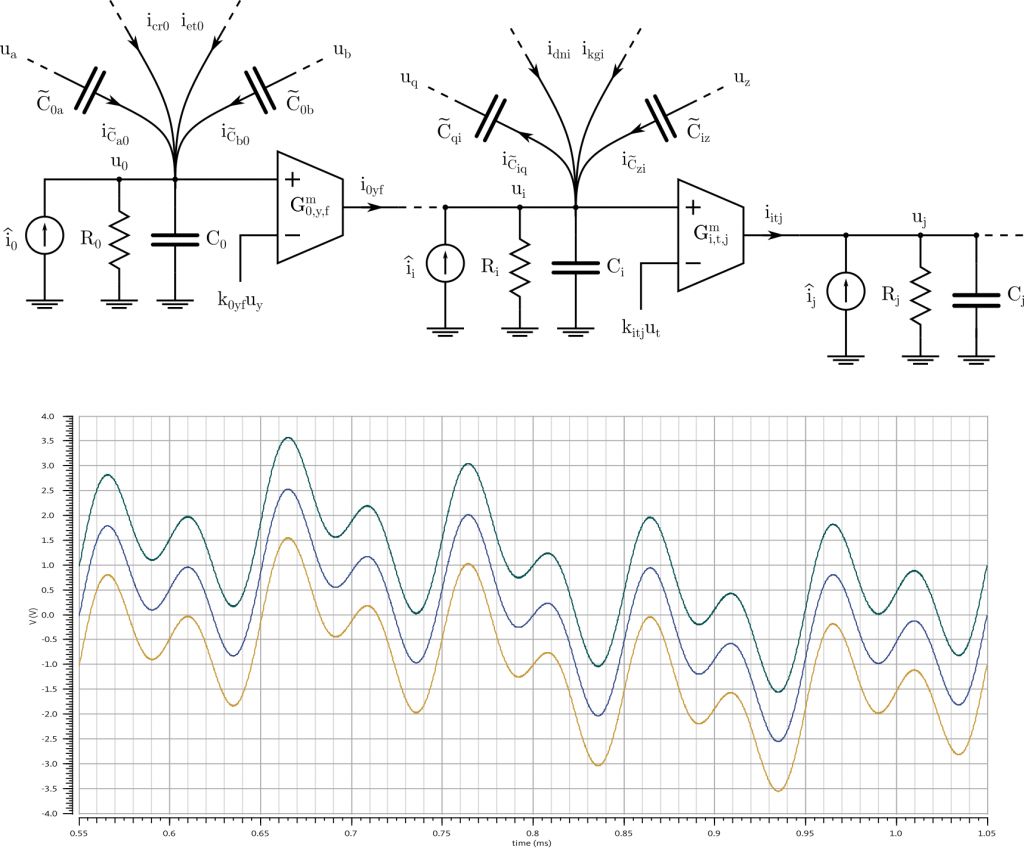

Abstract: This thesis deals with two different topics, both of which relate to the broader aspect of the linear behavior of circuits. The first part of the thesis presents methodologies for the estimation of harmonic distortion and intermodulation distortion that are applicable to linear CMOS circuits, while the second part presents a power stage architecture characterized by high linearity and efficiency. Harmonic and intermodulation distortion are two of the most important quantities that characterize the behavior of electronic circuits, and their estimation often proves to be a challenging task. Towards this direction, in the first thematic axis of the thesis, two systematic methods for the estimation of the aforementioned distortion types are presented. The proposed methods can be easily implemented in numerical computing environments and programming languages, are applicable to a wide variety of CMOS circuit topologies that exhibit weak nonlinear behavior, and offer high accuracy alongside with a fast computational profile. The methods rely on modeling a circuit as a structure of interconnected Gm-stages, where each one accurately captures the behavior of its corresponding circuit stage by means of an output current function dependent on its input, output voltages and cross-products of them. The distortion estimation is performed in the time-domain through two approximation steps, reducing the computational complexity and requiring only the solution of two systems of linear equations. The proposed methods are applied to various CMOS integrated circuit implementations in simulation environment, where their estimation accuracy and fast computational profile are validated. In the second thematic axis of the thesis, a power stage architecture characterized by high linearity and high efficiency is presented. The proposed architecture combines the excellent linearity of Class-A power stages with two continuously tracking supply rails that reduce power losses on the output devices while further improving the stage's linearity. The dynamic supply rails are generated by two DC-DC converters capable of producing tracking supply voltages of frequencies up to a few tens of kHz, making the topology suitable for audio applications or low-frequency signal measurements. The theoretical analysis of the proposed power stage architecture is accompanied by a proof-of-concept integrated CMOS implementation in simulation environment, where the characteristics and advantages of the architecture are illustrated.

Supervisor: Professor P.- P. Sotiriadis

PhD Student: Dimitrios Baxevanakis